- Indonesia

-

EnglishDeutschItaliaFrançais한국의русскийSvenskaNederlandespañolPortuguêspolskiSuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикGalegolietuviųMaoriRepublika e ShqipërisëالعربيةአማርኛAzərbaycanEesti VabariikEuskeraБеларусьLëtzebuergeschAyitiAfrikaansBosnaíslenskaCambodiaမြန်မာМонголулсМакедонскиmalaɡasʲພາສາລາວKurdîსაქართველოIsiXhosaفارسیisiZuluPilipinoසිංහලTürk diliTiếng ViệtहिंदीТоҷикӣاردوภาษาไทยO'zbekKongeriketবাংলা ভাষারChicheŵaSamoa日本語SesothoCрпскиKiswahiliУкраїнаनेपालीעִבְרִיתپښتوКыргыз тилиҚазақшаCatalàCorsaLatviešuHausaગુજરાતીಕನ್ನಡkannaḍaमराठी

E-mail:Info@YIC-Electronics.com

JK Flip Flop

Sandal jepit adalah komponen penting dalam sirkuit logika elektronik dan digital, memainkan peran penting dalam penyimpanan data dan kontrol bit biner (elemen dasar nol dan yang).Mereka merupakan bagian integral dari pengembangan sistem digital yang kompleks dan menemukan aplikasi di perangkat yang beragam seperti penghitung, register, perangkat penyimpanan, dan memori komputer.

Pengoperasian pemicu melibatkan urutan yang tepat.Mereka menyesuaikan status output mereka berdasarkan sinyal input yang mereka terima.Ketika flip-flop mendeteksi perubahan inputnya, ia mengubah outputnya sesuai.Kemudian menahan output yang stabil sampai sinyal input lain meminta perubahan.Kemampuan untuk merespons input dan menstabilkan output ini membuat flip-flop efektif untuk penyimpanan data dan operasi logika.

Katalog

Gambar 1: jk flip-flop

Memahami sandal jepit

Sandal jepit adalah dasar untuk mengendalikan data di sirkuit elektronik.Mereka memantau sinyal input untuk secara tepat mengontrol penyimpanan dan pemrosesan data.Ini bukan hanya tentang menyimpan data;Ini tentang membuat keputusan logis dan mengelola aliran data secara efisien.Misalnya, dalam sirkuit counter, flip-flop menghitung dari 0 ke 1 sebagai respons terhadap perubahan sinyal jam.Di sirkuit register, untuk sementara menyimpan data dari server untuk memastikan bahwa data stabil dan dapat diandalkan sebelum diproses lebih lanjut.

Sandal jepit bervariasi dalam desain dan fungsionalitasnya.

D Flip-flop menonjol karena kesederhanaan dan efektivitas sinkronisasi data mereka.Ini memiliki input data, berlabel D, yang mengambil data biner.Dengan masing-masing naik atau turun dari sinyal jam (tergantung pada desain), output cocok dengan input D. Ini membuat D flip-flop penting untuk register dan sistem memori sementara di mana data harus tetap disinkronkan.

Gambar 2: D Flip-Flop

T-flip-flop dikenal karena kemampuan switching mereka, dengan input tunggal T. Sinyal tinggi (logika 1) pada saat mengubah output pada setiap tepi sinyal clock yang valid, beralih dari 0 ke 1 dan sebaliknya.Ini membuatnya ideal untuk tugas -tugas seperti penghitungan biner dan divisi, yang penting untuk jam digital dan pengatur waktu.

Gambar 3: T flip-flop

Flip-flop RS adalah tipe paling sederhana dan menggunakan dua input (set dan reset) untuk secara langsung mengontrol outputnya.Set membuat output tinggi, reset membuatnya rendah.Jika kedua input tinggi, output menjadi tidak terdefinisi, yang merupakan kelemahan dari desain dasarnya.

Gambar 4: RS Flip-Flop

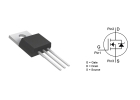

JK Flip-Flop adalah peningkatan pada flip-flop RS, dengan dua input J dan K, Mirror Set, dan Fungsi Reset.Yang istimewa tentang itu adalah perilakunya ketika kedua input tinggi: output beralih dengan setiap siklus clock aktif, daripada berada dalam keadaan yang tidak terdefinisi.Fitur ini memperluas penggunaannya dalam kontrol logika yang kompleks dan mekanisme waktu yang tepat.

Gambar 5: jk flip-flop

Setiap tipe pemicu menawarkan fitur unik yang cocok untuk aplikasi yang berbeda.Dari sinkronisasi data dalam flip-flop dan switching dalam flip-flop, ke fungsi set/reset sederhana dalam sandal jepit RS dan fleksibilitas yang ditingkatkan dari jk-flop, insinyur dapat memilih tipe yang paling cocok berdasarkan persyaratan sirkuit mereka.JK Flip-Flops terutama menonjol karena keserbagunaan mereka dalam desain digital, secara efektif mengelola ketidakpastian yang umum di sirkuit logika digital.

Pandangan terperinci di jk flip-flop

Flip-flop JK meningkatkan fungsionalitas flip-flop tradisional dengan menyelesaikan ambiguitas dalam output ketika kedua terminal input aktif.Ini memperkenalkan mekanisme yang memungkinkannya untuk mengelola input tinggi simultan dari J (set) dan K (reset) tanpa jatuh ke keadaan yang tidak ditentukan.

Saat menggunakan jk flip-flop, operator mengalami proses yang jelas dan mudah dalam mengatur dan mengatur ulang sirkuit.Input J dan K secara aktif mengontrol output.Berbeda dengan flip-flop RS, yang hanya dapat mengatur atau mengatur ulang dengan sukses jika inputnya tidak tinggi pada saat yang sama, model JK menangani sinyal tinggi bersamaan dengan lancar.Begini cara kerjanya: Setelah menerima sinyal jam, jika J dan K tinggi, flip-flop mengubah outputnya.Ini berarti sakelar output antara 0 dan 1, atau sebaliknya, secara efektif menghindari hasil yang tidak pasti dan meningkatkan reliabilitas sirkuit.

Flip-flop ini tidak hanya mengelola tugas logika dasar tetapi juga beradaptasi dengan desain yang kompleks karena kemampuannya untuk beralih.Toggling dipicu oleh tepi sinyal jam, yang menyelaraskan tindakan flip-flop dengan waktu yang tepat yang diperlukan dalam sistem digital canggih.Apakah itu dalam pengaturan pemrosesan data yang serba cepat yang menuntut waktu yang tajam atau dalam sistem penyimpanan yang stabil yang harus secara andal mempertahankan keadaan mereka, flip-flop JK memastikan kinerja yang konsisten.

Desain jk flip-flop dirancang untuk skenario yang membutuhkan kontrol dan presisi keadaan yang kuat.Dengan mengelola dengan hati-hati bagaimana input J dan K diperlakukan, flip-flop memungkinkan desainer untuk membuat fungsi logika canggih dan skema manajemen negara.Kemampuan beradaptasi ini menjadikan JK Flip-Flop komponen yang sangat diperlukan dalam sirkuit elektronik yang kompleks, memberikan solusi yang dapat diandalkan untuk masalah ketidakpastian keadaan yang biasa dihadapi dalam desain logika digital.

Konten pada fungsionalitas jk flip-flop

JK Flip-Flops memainkan peran penting dalam menyimpan dan mengonversi informasi biner di sirkuit logika digital karena keserbagunaan dan keandalannya.Mereka memiliki dua terminal input berlabel J dan K, input clock (CLK), dan dua output.terminal (q dan ~ q).Kunci operasinya adalah kontrol yang tepat dari terminal ini, memungkinkan flip-flop untuk memperbarui outputnya secara sinkron dengan perubahan sinyal jam dan input di J dan K.

JK Flip-Flops pada awalnya dirancang untuk menyelesaikan ketidakpastian output dalam sandal jepit RS (seperti konflik negara ketika kedua sinyal yang ditetapkan dan reset ditegaskan) dan menggabungkan logika untuk mengelola situasi tersebut secara efisien.Ini tidak hanya mempertahankan fungsi dasar dari flip-flop RS tetapi juga meningkatkan fleksibilitas dan stabilitas flip-flop RS.Ini membuatnya sangat efisien dalam memecahkan tantangan logika digital yang kompleks.

Ketika input J dan K keduanya 0, flip-flop mempertahankan keadaan saat ini, memastikan retensi data yang stabil.

Ketika J diatur ke 1 dan K diatur ke 0, output Q diatur ke 1, menunjukkan fungsi pengaturan yang kuat.

Ketika J adalah 0 dan k diatur ke 1, flip-flop reset dan output Q beralih ke 0, melakukan fungsi reset dasarnya.

Ketika kedua input adalah 1, flip-flop beralih keadaan.Jika q adalah 0, menjadi 1, jika 1, ia beralih ke 0. Jenis switching ini membutuhkan aplikasi dengan perubahan keadaan yang sering.

Desainnya juga menekankan waktu yang tepat.Ini menggunakan mekanisme yang dipicu tepi untuk memperbarui keadaan pada saat yang tepat dari tepi sinyal jam, baik positif maupun negatif.Akurasi ini penting untuk sistem yang membutuhkan waktu yang ketat, seperti transfer data sinkron dan analisis waktu.

Untuk peningkatan kegunaan dan fleksibilitas, beberapa model flip-flop JK mencakup fungsionalitas set langsung (set) dan reset (reset).Ini memungkinkan kontrol langsung dari status output tanpa menunggu sinyal clock, menyederhanakan operasi dalam skenario tertentu dan memberikan respons cepat dalam situasi darurat.Fitur ini menambah nilai praktis yang signifikan, membuatnya lebih mudah untuk dikelola dan dengan cepat menyesuaikan sirkuit digital.

Tabel kebenaran jk flip-flop

JK Flip-Flop karena keserbagunaannya di sirkuit digital dapat dipahami melalui tabel kebenarannya.Tabel dengan jelas menguraikan bagaimana keadaan output berubah dalam berbagai kondisi input, menunjukkan kemampuan beradaptasi dan keandalannya dalam desain sirkuit.

Inti dari pengoperasian jk flip-flop adalah responsnya terhadap sinyal jam CLK.Tabel kebenaran mengatur operasi ini dengan merinci keadaan output Q dan komplemennya berdasarkan input di terminal J dan K selama setiap tepi aktif CLK.Kolom "Q (sebelum)" menunjukkan keadaan sebelumnya dari flip-flop sebelum sinyal CLK tiba.Saat CLK diaktifkan, pembaruan kolom "Q (setelah)" untuk mencerminkan status baru.

Secara khusus, ketika input J dan K keduanya diatur tinggi (1), output Q sakelar;Jika Q adalah 0, beralih ke 1, jika 1, ia beralih ke 0. Kemampuan switching ini penting untuk merancang sirkuit logika canggih yang mengandalkan inversi keadaan, seperti berbagai penghitung.

Gambar 6: Tabel kebenaran untuk fungsi JK

Penting juga untuk dicatat bahwa kinerja jk flip-flop dapat bervariasi tergantung pada tepi pemicu yang dipilih (positif atau negatif) dan perangkat keras yang digunakan.Desainer harus memilih tepi pemicu yang benar dan mengoptimalkan perangkat keras untuk memenuhi kebutuhan sirkuit dan mencapai fungsionalitas logika yang diharapkan.

Selain itu, jk flip-flop mendukung waktu yang kompleks dan operasi logika dengan secara tepat mengendalikan keadaan input yang disinkronkan dengan sinyal jam.Akurasi ini membuatnya ideal untuk sistem digital presisi tinggi berkecepatan tinggi.Selain itu, desainnya memungkinkan perubahan keadaan cepat melalui sinyal kontrol eksternal, sehingga meningkatkan keserbagunaannya dalam situasi di mana respons cepat atau penyesuaian keadaan darurat diperlukan.

Singkatnya, jk flip-flop adalah dasar dari desain sirkuit digital karena kinerjanya yang andal dalam berbagai fungsi dari kontrol memori sederhana hingga penghitung kompleks dan sistem waktu.Desainnya memungkinkan sistem elektronik untuk beroperasi secara efisien dan stabil, memaksimalkan potensi logika digital.

Flip-flop-slave-slave dalam elektronik digital

Flip-flop-master-slave adalah elemen penting dalam elektronik digital, yang dirancang khusus untuk mengatasi masalah osilasi transien yang terlihat dengan sandal jepit JK standar di bawah kondisi input yang berubah dengan cepat.Osilasi semacam itu biasanya muncul dalam durasi aktif sinyal jam, menyebabkan keadaan output berfluktuasi secara tidak terduga.

Untuk melawan ketidakstabilan ini, konfigurasi master-slave menggunakan arsitektur flip-flop ganda: satu "master" dan satu "budak."Pengaturan ini memungkinkan perangkat untuk menyelesaikan pembaruan ke status dalam satu siklus clock, sehingga secara signifikan meningkatkan keandalan dan stabilitas sirkuit digital.

Secara operasional, fungsi flip-flop-jk-slave-slave dalam dua fase berbeda: fase penangkapan dan fase kait.Setiap fase sesuai dengan tepi sinyal jam yang berbeda, dirancang dengan cerdik untuk menangani input dan menstabilkan output.

Fase Capture: Pada tepi yang naik dari sinyal jam, master flip-flop menangkap nilai input saat ini dari input J dan K dan mengamankan keadaan internalnya.Keadaan yang ditangkap ini tidak segera dikirim ke output.

Fase kait: Mengikuti tangkapan, di tepi jatuh jam, slave flip-flop mengambil dan mengunci dalam keadaan master dari fase penangkapan.Kemudian mentransmisikan status ini ke output utama flip-flop.Akibatnya, pembaruan aktual untuk output hanya terjadi setelah seluruh siklus clock selesai, sehingga menstabilkan output.

Memanfaatkan sandal jk-master-slave JK memungkinkan desainer untuk memanfaatkan setiap tepi sinyal jam untuk secara terpisah mengelola aktivitas sandal jepit master dan slave, mencapai fungsionalitas yang dipicu oleh tepi yang sebenarnya.Pendekatan ini secara efektif menghilangkan osilasi output sementara yang dipicu oleh perubahan input yang cepat, memastikan stabilitas dan keandalan output, bahkan di bawah kondisi berkecepatan tinggi.

Selain itu, arsitektur master-slave tidak hanya meningkatkan sinkronisasi dalam sirkuit tetapi juga meningkatkan stabilitas keseluruhan sistem.Karena keadaan output tetap tidak terpengaruh oleh perubahan input apa pun sampai akhir siklus clock, flip-flop-master-slave terbukti sangat efektif untuk logika digital dan aplikasi kontrol waktu yang kompleks.

Gambar 7: Master-Slave JK Flip-Flop

The Dual JK Flip-Flop 74LS73

Sirkuit terintegrasi 74LS73 adalah elemen kunci dalam 74 seri perangkat logika dan terkenal karena menampung dua sandal jepit JK independen.Desain flip-flop ganda ini penting untuk menghemat ruang papan sambil meningkatkan fungsionalitas dan fleksibilitas sistem digital yang kompleks.Setiap flip-flop memiliki input J dan K sendiri, input clock (CLK), dan reset (r) input, memungkinkannya untuk memproses sinyal dan melakukan operasi logika secara mandiri.

Gambar 8: Tampilan Top Dual JK Flip-Flop 74LS73

Chip ini sangat efektif untuk aplikasi yang perlu menangani logika saluran ganda.Ini sangat ideal untuk mengelola dua set sinyal independen secara bersamaan atau membuat sirkuit logika berurutan yang kompleks seperti penghitung ganda, pembagi frekuensi, atau sirkuit kontrol spesifik yang disinkronkan.Dimasukkannya dalam keluarga pemicu Schmitt berdaya rendah menyoroti fokus desainnya pada konsumsi daya rendah, membuatnya ideal untuk aplikasi yang sensitif terhadap energi.

Fitur menonjol dari setiap flip-flop pada chip 74LS73 adalah kemampuannya yang jelas langsung.Dengan memanfaatkan input reset (r), keadaan output dapat segera diatur ulang ke 0 terlepas dari keadaan saat ini dari input J dan K.

Flip-flop di 74LS73 menembak di tepi yang naik dari sinyal jam, memastikan kontrol waktu yang tepat.Desain memastikan karakteristik respons yang stabil pada frekuensi operasi yang berbeda, yang bermanfaat untuk mempertahankan pembaruan logika yang akurat yang disinkronkan dengan sinyal jam.Presisi semacam ini sangat penting dalam bidang yang membutuhkan waktu yang ketat, seperti komunikasi digital, mekanisme waktu yang tepat, dan berbagai sistem kontrol otomatis.

74LS73 mengintegrasikan dua jk-flip-flop pada chip tunggal, meningkatkan integrasi desain sistem dan memberikan desainer sirkuit dengan fleksibilitas yang lebih besar.Pengaturan ini tidak hanya mengurangi jejak fisik dewan, tetapi juga menyederhanakan proses desain dan debugging, sehingga meningkatkan keandalan dan kinerja sistem secara keseluruhan.Akibatnya, 74LS73 menjadi sumber yang berharga bagi desainer sirkuit digital, terutama bermanfaat untuk proyek yang membutuhkan kontrol dan kemampuan beradaptasi.

IC flip-flop jk beragam untuk desain sirkuit

Sandal jepit JK penting karena keserbagunaannya dalam desain sirkuit digital.Selain 74LS73 standar, beberapa sirkuit terintegrasi (ICS) JK Flip-Flip lainnya menawarkan fitur dan aplikasi yang unik.Di bawah ini adalah tampilan terperinci pada beberapa model populer, masing -masing menawarkan manfaat spesifik kepada desainer sirkuit.

74LS76: Flip-flop ganda ini memperluas fungsionalitas dasar 74LS73 dengan memasukkan input set dan reset independen dan input clock terpisah untuk setiap flip-flop.Peningkatan ini memberi desainer kontrol yang tepat atas setiap peristiwa pemicu.74LS76 sangat berharga dalam skenario kompleks di mana kontrol waktu independen di dua saluran logika penting.

Gambar 9: 74LS76

74LS107: 74LS107 menggunakan mekanisme pemicu tepi jatuh, termasuk dua sandal jk jk, masing-masing dengan input JK J, K, CLK, dan reset independen.IC ini sangat cocok untuk skenario yang memerlukan pengalihan logika pada tepi jatuh dari sinyal clock, sehingga meningkatkan efisiensi dan akurasi mengelola logika yang dipicu oleh tepi yang jatuh.

Gambar 10: 74LS107

74LS112: Dikenal karena kinerjanya tinggi, 74LS112 menawarkan pemicu dua arah yang merespons tepi positif dan negatif.Ini juga mencakup fungsi yang telah ditetapkan dan jelas.Fitur-fitur ini membuat 74LS112 cocok untuk aplikasi yang menuntut yang membutuhkan operasi cepat dan kontrol waktu yang kompleks, seperti penghitung kecepatan tinggi dan sistem sinkronisasi yang kompleks.

Gambar 11: 74LS112

CD4027: Bagian dari keluarga Teknologi CMOS, CD4027 adalah flip flip-flop J-K dual-K yang beroperasi pada rentang tegangan yang luas dan menawarkan konsumsi daya rendah.Ini memiliki set independen, reset, j, k, dan input jam dan output komplementer.CD4027 sangat ideal untuk peralatan bertenaga baterai dan aplikasi power-sensitive lainnya.

Gambar 12: CD4027

SN74HC73: Keluarga CMOS berkecepatan tinggi ini dari sandal jk jk independen ganda ini dirancang untuk sistem yang membutuhkan kecepatan tinggi dan konsumsi daya rendah.SN74HC73 sangat cocok untuk sistem elektronik kinerja tinggi modern seperti peralatan komunikasi berkecepatan tinggi dan mekanisme kontrol presisi.

Gambar 13: SN74HC73

Konfigurasi Master-Slave di Sirkuit Elektronik

Konfigurasi master-slave memainkan peran penting dalam sirkuit elektronik dan desain logika digital, terutama dalam pengoperasian flip-flop.Konfigurasi ini menggunakan dua sandal jepit: satu ditunjuk sebagai master dan yang lainnya sebagai budak.Master flip-flop menangkap sinyal yang masuk di bawah panduan sinyal jam, menahan data sementara.Bersamaan dengan itu, slave flip-flop tetap tidak aktif, menunggu gilirannya.

Saat sinyal jam berubah ke tepi yang berlawanan, peran bergeser secara dinamis.Slave Flip-Flop mengaktifkan, membaca dan mengunci keadaan data yang ditetapkan oleh master.Kemudian mengeluarkan keadaan ini, memastikan bahwa setiap perubahan selanjutnya dalam input setelah penangkapan master tidak mempengaruhi output siklus ini.Pemisahan fase penangkapan dan output ini meminimalkan osilasi output dan membantu menjaga stabilitas dan keandalan sinyal, mendukung kinerja yang konsisten.

Gambar 14: Konfigurasi Master-Slave

Operasi strategis dalam pengaturan master-slave ini memungkinkan kontrol yang disetel dengan baik atas pemrosesan sinyal.Dengan memanfaatkan dua tepi yang berbeda dari sinyal jam, master flip-flop merespons satu tepi untuk mengamankan keadaan sinyal.Sementara itu, slave flip-flop menggunakan tepi yang berlawanan untuk mengeluarkan data.Kontrol berbasis tepi yang tepat ini membantu mencegah gangguan langsung dalam output karena perubahan status master, menjaga integritas output sampai siklus berikutnya dimulai.

Di luar meningkatkan stabilitas sinyal, konfigurasi master-slave meningkatkan fleksibilitas dan keandalan desain sirkuit.Ini mendukung pemrosesan data yang kompleks dan fungsi kontrol logika, memainkan peran kunci dalam penghitung digital, register, dan sistem transfer data berkecepatan tinggi.Pengaturan ini memastikan sinkronisasi data dan waktu yang akurat, memainkan peran kunci dalam operasi frekuensi tinggi di mana output stabil diperlukan.

Konfigurasi master-slave mengatasi tantangan umum dalam desain sirkuit, seperti menangani sinyal berkecepatan tinggi tanpa kehilangan kinerja.Ini mencegah kesalahan data dan ketidakstabilan sistem yang dapat muncul dari perubahan sinyal input yang cepat.Dengan struktur dan prinsip operasional yang unik, konfigurasi master-slave meningkatkan stabilitas dan keandalan sistem sistem secara keseluruhan, menawarkan desainer kontrol dan fleksibilitas yang lebih besar dalam mengatasi tantangan desain logika digital yang kompleks.

Memanfaatkan sandal jk jk dalam desain sirkuit digital

Sandal jepit JK terkenal karena keserbagunaannya dalam desain sirkuit digital, berfungsi sebagai komponen utama untuk mengimplementasikan fungsionalitas tingkat lanjut.Sandal jepit ini melampaui tugas penyimpanan dasar, memungkinkan pembuatan kontrol waktu yang kompleks dan sirkuit pengambilan keputusan logis.

Salah satu penggunaan klasik jk-flop-flop adalah dalam membangun penghitung biner.Insinyur menghubungkan beberapa jk-flip-flop secara seri untuk membentuk rantai penghitungan.Setiap output flip-flop menautkan langsung ke input jam dari flip-flop berikutnya.Dengan mengatur input J dan K ke tinggi, setiap flip-flop mengubah outputnya dengan setiap pulsa clock, secara efektif menghitung dari 0 ke nilai maksimum yang telah ditentukan.Pengaturan ini mendukung tidak hanya waktu dasar tetapi juga aplikasi seperti penghitungan acara dan pengukuran frekuensi, memainkan peran kunci dalam waktu digital dan penghitungan fungsi.

Selain itu, jk-flip-flop adalah kunci dalam membangun pembagi frekuensi.Cukup mengatur input J dan K yang tinggi memungkinkan output flip-flop untuk beralih setiap kali sinyal jam diaktifkan, sehingga mengurangi separuh frekuensi sinyal clock.Fungsi divide-by-2 ini dapat diperluas dengan menambahkan lebih banyak jk-flip-flop secara seri, memungkinkan penciptaan berbagai rasio divisi frekuensi.Kemampuan ini mendukung pembuatan frekuensi clock yang berbeda dan sinkronisasi sistem dalam komunikasi digital dan pemrosesan sinyal.

Selain itu, sandal jepit JK signifikan dalam desain register shift.Register Shift mengelola data secara berurutan, mendukung input dan penyimpanan sementara bit data.Fungsionalitas ini mendukung tugas -tugas seperti transmisi data, pemrosesan sinyal, dan buffering data sementara.Sifat yang dapat dikonfigurasi dari jk flip-flops memungkinkan untuk manipulasi bit data yang tepat, meningkatkan fleksibilitas dan efisiensi desain sirkuit.

Aplikasi signifikan lain dari jk-flop-flop adalah dalam mengembangkan mesin status terbatas (FSM).FSM adalah sirkuit logika yang transisi antara status dan output berdasarkan sinyal input dan status arus.Pengaturan ini mendukung tugas pengambilan keputusan dan kontrol logis yang kompleks.Dengan mengintegrasikan jk-flip-flop dengan gerbang logika lainnya, desainer dapat menyusun sirkuit yang mampu menangani pola input yang rumit dan melaksanakan operasi logika yang komprehensif.Desain seperti itu mendasar dalam sistem kontrol otomatis, protokol komunikasi digital, dan pemrosesan data yang canggih.

Terakhir, jk-flip-flop juga merupakan kunci untuk menerapkan logika kontrol sinkron dan asinkron dalam sirkuit.Mereka memastikan sinkronisasi operasi sistem yang tepat, mempertahankan urutan logis yang konsisten di seluruh sistem.Fleksibilitas jk-flip-flop juga membantu dalam deteksi dan koreksi kesalahan waktu, yang mendukung operasi sistem yang stabil dan keakuratan transmisi data.Ini membuat jk flip-flop tidak berharga untuk meningkatkan keandalan sistem dan efisiensi operasional di lingkungan digital yang kompleks.

Kesimpulan

Flip-flop telah memperkuat statusnya sebagai elemen mendasar dalam desain sirkuit digital, terbukti sangat diperlukan untuk mencapai operasi logika digital yang efisien dan andal.Komponen -komponen ini menangani berbagai fungsi, dari penyimpanan data sederhana dan menghitung hingga logika kontrol yang lebih kompleks dan tugas pemrosesan data.Kemampuan mereka untuk memberikan solusi yang efektif dan andal mendukung kebutuhan desain elektronik modern yang terus berubah.

JK memicu terutama menonjol karena fleksibilitas dan keserbagunaan mereka.Di tangan seorang desainer sirkuit digital yang terampil, berfungsi hampir seperti kunci utama, membuka kunci potensi untuk desain sirkuit yang efisien dan stabil.Perannya melampaui operasi dasar, memfasilitasi proses kompleks untuk meningkatkan fungsionalitas dan keandalan sistem elektronik.

Pertanyaan yang Sering Diajukan [FAQ]

1. Apa sandal sandal SR dan J-K?

JK Flip-Flop adalah perangkat yang kompleks di mana kedua input diatur ke High menghasilkan output yang beralih antara tinggi dan rendah.Sakelar ini terjadi setiap kali input diadakan pada 1, memungkinkan perubahan keadaan dinamis.Di sisi lain, flip-flop-flop menghadapi batasan di mana memiliki kedua input tinggi mengarah ke keadaan tidak valid, masalah yang dihindari oleh jk flip-flop dengan cerdik.

2. Apa flip-flop yang dijelaskan?

Flip-flop pada dasarnya adalah sirkuit bistable, yang berarti dapat berada secara stabil di salah satu dari dua negara yang mungkin.Fungsi sebagai unit memori dasar, mempertahankan informasi keadaan dalam pengaturan fisiknya.Keadaan sirkuit dapat diubah oleh sinyal yang diterapkan pada input kontrolnya, yang mengelola transisi antar negara.

3. Apa perbedaan antara jk flip flop dan kait?

JK Flip-Flop memodifikasi outputnya secara eksklusif sebagai respons terhadap pulsa clock yang bertepatan dengan perubahan input, menjadikannya perangkat sinkron.Sebaliknya, kait mengubah outputnya secara langsung sebagai respons terhadap perubahan input, beroperasi secara tidak sinkron tanpa perlu pulsa jam untuk memicu perubahan keadaan.

4. Apa keuntungan utama menggunakan jk flip-flop?

JK Flip-Flops sangat menguntungkan di sirkuit counter asinkron.Kemampuan switching mereka (keadaan output membalik dengan masing -masing pulsa clock input) memungkinkan mereka untuk secara efektif mengurangi separuh frekuensi clock input.Fitur ini memungkinkan desain penghitung biner dan urutan penghitungan kompleks lainnya dan pemanfaatan kemampuan switching yang tepat.

5. Apa segitiga di j-k flip-flop?

Segitiga kecil pada input jam dari flip-flop JK melambangkan sifatnya yang dipicu tepi, yang berarti bahwa ia merespons secara akurat terhadap perubahan di tepi pulsa jam.Gelembung pada input ini menunjukkan sensitivitas terhadap tepi jatuh (tepi jatuh), sementara tidak ada gelembung yang menyiratkan respons terhadap peningkatan tepi (tepi naik).Detail ini berguna untuk memahami bagaimana flip-flop berinteraksi dengan sinyal jam dan mempengaruhi perilakunya di sirkuit.

Blog terkait

-

Dasar-dasar sirkuit op-amp

2023/12/28

Dalam dunia elektronik yang rumit, sebuah perjalanan ke misteri selalu membawa kita ke kaleidoskop komponen sirkuit, baik yang indah maupun kompleks.D... -

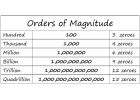

Berapa nol dalam sejuta, miliar, triliun?

2024/07/29

Juta mewakili 106, sosok yang mudah dipahami jika dibandingkan dengan barang sehari -hari atau gaji tahunan. Miliar, setara dengan 109, mulai meregang... -

Panduan Komprehensif untuk SCR (penyearah yang dikendalikan silikon)

2024/04/22

Silicon Controlled Rectifiers (SCR), atau Thyristors, memainkan peran penting dalam teknologi elektronik daya karena kinerja dan keandalannya.Artikel ... -

Baterai Lithium-Ion CR2032: Aplikasi Multi-Scenario dan Keuntungan Uniknya

2024/01/25

Baterai CR2032, baterai lithium-ion berbentuk koin yang umum digunakan, sangat penting pada banyak produk listrik berdaya rendah seperti jam tangan di... -

Transistor NPN dan PNP

2023/12/28

Untuk menjelajahi dunia teknologi elektronik modern, memahami prinsip -prinsip dasar dan aplikasi transistor sangat penting.Meskipun transistor tipe N... -

Apa itu termistor

2023/12/28

Di ranah teknologi elektronik modern, mempelajari sifat dan mekanisme kerja termistor menjadi upaya penting.Komponen elektronik presisi dan sangat mud... -

Jelajahi perbedaan antara PCB dan PCBA

2024/04/16

PCB berfungsi sebagai tulang punggung perangkat elektronik.Terbuat dari bahan non-konduktif, secara fisik mendukung komponen sementara juga menghubung... -

BC547 Transistor Comprehensive Guide

2024/07/4

Transistor BC547 umumnya digunakan dalam berbagai aplikasi elektronik, mulai dari amplifier sinyal dasar hingga sirkuit osilator yang kompleks dan sis... -

Apa itu sakelar solenoid

2023/12/26

Ketika arus listrik mengalir melalui koil, medan magnet yang dihasilkan menarik atau mengusir inti besi, menyebabkannya bergerak dan membuka atau menu... -

IRLZ44N MOSFET DataTheet, sirkuit, setara, pinout

2024/08/28

IRLZ44N adalah MOSFET N-Channel Power yang banyak digunakan.Terkenal dengan kemampuan switching yang sangat baik, sangat cocok untuk berbagai aplikasi...

Bagian panas

- AD7398BRUZ

- 1206YC104KAT2A

- UC3524ADWTR

- EP901PBF

- M50FLW080AK5

- CX24227-11Z

- XH3A-0141-4A

- ADATE303BBCZ

- P6928BIZPH

- 06031A2R7DAT2A

- SKKT105/16E

- SM72375MM/NOPB

- STD16N50M2

- 5CGXFC5C6F23I7N

- UC3714DP

- HIP1011CBZA-T

- TAS5707PHP

- CC2564MODNCMOER

- EDB4432BBPA-1D-F-D

- DS1963S-F5+

- S71PL032J40BAW0K0

- MK24FN1MOVLL12

- NT1721-RWK

- 08055A101GAT4A

- EP1C3T144C6

- RT1206DRE0747KL

- TC7117CLW

- BT134W-600D

- TPS61254YFFR

- SPMC65SF112A

- TMS320C50PQA57

- MX29L001MC-10

- GS8120-174-004DCOZ

- BR24G32FVT

- EPM7032SLC44-7

- TNETD5080GGW

- STE101P-1A

- S8F19S1065

- 2225AC302KAT1A

- T491A105M016ZTAC00

- T491D337K006AT4860

- CY7C428-25JC

- FC1610-BC-AK

- PEB2084QUAT-SV1.3

- NT71912MBG-S

- MB96395RSAPMC-GS-108E2

- VI-912047B

- 74HC1G14GW-Q100