- Indonesia

-

EnglishDeutschItaliaFrançais한국의русскийSvenskaNederlandespañolPortuguêspolskiSuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикGalegolietuviųMaoriRepublika e ShqipërisëالعربيةአማርኛAzərbaycanEesti VabariikEuskeraБеларусьLëtzebuergeschAyitiAfrikaansBosnaíslenskaCambodiaမြန်မာМонголулсМакедонскиmalaɡasʲພາສາລາວKurdîსაქართველოIsiXhosaفارسیisiZuluPilipinoසිංහලTürk diliTiếng ViệtहिंदीТоҷикӣاردوภาษาไทยO'zbekKongeriketবাংলা ভাষারChicheŵaSamoa日本語SesothoCрпскиKiswahiliУкраїнаनेपालीעִבְרִיתپښتوКыргыз тилиҚазақшаCatalàCorsaLatviešuHausaગુજરાતીಕನ್ನಡkannaḍaमराठी

Penskalaan dan miniaturisasi CMOS: kinerja, kekuatan, dan keandalan

Katalog

Model Perangkat Pemurnian

Mencapai hasil desain yang luar biasa tergantung pada keakuratan dan luasnya model perangkat yang memperhitungkan berbagai proses dan kondisi.Mengintegrasikan bahan-bahan inovatif, seperti dielektrik K tinggi dan gerbang logam, ke dalam struktur CMOS konvensional memperkaya model-model ini dengan menawarkan sifat listrik yang ditingkatkan.Integrasi ini mendorong teknik desain inventif.Transisi untuk menggunakan bahan -bahan baru ini memainkan peran formatif dalam mengembangkan model perangkat, menunjukkan janji untuk arus bocor yang diminimalkan dan potensi yang unggul untuk meningkatkan arus drive.Kemajuan semacam itu merangsang pertumbuhan desain kompetitif dalam lanskap teknologi modern.Veteran industri mengakui bahwa pemahaman yang mendalam tentang bahan -bahan ini melibatkan siklus pengujian dan model kalibrasi yang menyeluruh untuk secara andal mencerminkan perilaku dan interaksi yang rumit dalam perangkat.

Evolusi penskalaan teknologi

Transformasi dalam penskalaan CMOS telah mengkatalisasi inovasi kompleks dalam industri elektronik, memfasilitasi kemajuan yang mulus dan gesit dalam integrasi.Mengejar kinerja yang dipercepat di samping peningkatan kepadatan integrasi mendorong fokus yang intens pada ketepatan parameter perangkat penskalaan.Penyesuaian terperinci ini mencakup elemen -elemen seperti resolusi litografi, panjang saluran yang efektif, ketebalan dielektrik gerbang, tegangan pasokan, dan perilaku kebocoran perangkat.Karena panjang saluran perangkat CMOS berkurang, lonjakan kinerja dan penggunaan energi per transisi menurun secara nyata, berkontribusi pada peningkatan efisiensi dan kekompakan.

Gambar 1. Tren VDD tegangan catu daya, voltase ambang VTH, dan tox ketebalan oksida gerbang relatif terhadap panjang saluran perangkat CMOS

Dampak penskalaan pada efisiensi sirkuit

Mencapai mikroprosesor superior dan kinerja memori didukung oleh kemajuan penskalaan transistor yang signifikan:

- Node IC CMOS menjalani pengurangan penskalaan 30%, penurunan penundaan gerbang sekitar 30% dan dengan demikian meningkatkan frekuensi clock maksimum sebesar 43%.

- Kepadatan perangkat mengalami efek penggandaan.

- Kapasitansi parasit berkurang 30% karena metodologi penskalaan.

- Energi dan daya aktif per transisi dikurangi masing -masing sebesar 65% dan 50%.

Gambar 2. Tren kinerja CMOS, kepadatan daya, dan kepadatan sirkuit

Pengaruh penskalaan pada disipasi kekuasaan

Dalam perangkat CMOS, daya dinamis dan arus kebocoran muncul sebagai sumber konsumsi daya yang signifikan.Pengurangan tegangan ambang batas, didorong oleh penskalaan teknologi canggih, menonjolkan pentingnya konsumsi daya kebocoran.Suhu memainkan peran yang lebih substansial dalam memengaruhi daya bocor bila dibandingkan dengan penggunaan daya aktif, menghasilkan peningkatan daya bocor yang signifikan.

Ilustrasi di bawah ini menguraikan dinamika antara konsumsi daya dinamis vs kebocoran, dengan pakta melambangkan daya dinamis dan punggung daya bocor yang menandakan.

Gambar 3. Dinamika daya aktif dan kebocoran untuk ukuran die konstan

Penskalaan dan pengaruhnya terhadap keandalan

Dorongan untuk mengurangi tegangan catu daya dalam teknologi skala termasuk kebutuhan untuk mengurangi medan listrik internal di dalam perangkat sementara juga mengurangi konsumsi daya aktif.Karena hubungan di mana daya aktif sebanding dengan VDD², pengurangan VDD menyiratkan penyesuaian yang diperlukan untuk VTH untuk memberikan overdrive arus saluran yang diinginkan untuk fungsionalitas yang optimal.Namun, VTH yang lebih rendah meningkatkan arus kebocoran di luar negara, menghadirkan rintangan untuk teknologi skala nanometer.

Kekhawatiran reliabilitas jangka panjang yang menonjol melibatkan kerusakan dielektrik yang bergantung pada waktu (TDDB) dari dielektrik gerbang, injeksi pembawa panas (HCI), ketidakstabilan suhu bias negatif (NBTI), elektromigrasi (EM), dan kekosongan yang diinduksi stres (SIV).Selama tiga dekade, fisika yang kompleks, karakterisasi, dan pemodelan terperinci dari fenomena ini telah menjadi pusat upaya penelitian.

Meningkatkan teknik tegangan suplai

Menjelajahi metode untuk memperbaiki tegangan pasokan mengungkap strategi menawan yang meningkatkan efisiensi dengan mempengaruhi konsumsi energi secara signifikan.Dengan secara sadar mengurangi tegangan pasokan, penurunan kuadratik yang jelas dalam daya switching diamati, menawarkan keunggulan strategis dalam optimasi daya.Pendekatan ini juga menangani masalah saat ini, secara efektif mengurangi efek penghalang yang diinduksi drainase (DIBL)-area fokus dalam elektronik modern.

Gambar 4. Gerbang oksida bocor arus versus catu daya

Variasi penskalaan tegangan pasokan

Penyesuaian statis yang disesuaikan

Penskalaan tegangan suplai statis melibatkan tweak yang telah ditentukan yang disesuaikan untuk jalur atau komponen sirkuit tertentu.Teknik ini terbukti menguntungkan untuk tugas -tugas dengan kebutuhan daya yang stabil, karena memungkinkan pasokan tegangan tepat disesuaikan agar sesuai dengan kebutuhan energi yang beragam.Dengan menggunakan pengaturan tegangan yang telah ditentukan, penggunaan energi dioptimalkan sambil mempertahankan keandalan sistem, terutama menarik bagi para insinyur yang berfokus pada kinerja yang stabil namun menginginkan efisiensi energi yang tinggi.Perhitungan penyesuaian ini membawa kepuasan halus yang mirip dengan memenuhi tujuan energi yang terdefinisi dengan baik.

Penyesuaian dinamis yang responsif

Dynamic Supply Voltage Scaling (DVFS) menawarkan pendekatan serbaguna, memungkinkan perubahan tegangan waktu nyata dalam menanggapi permintaan kinerja yang mengalihkan.Strategi yang fleksibel ini mencapai keseimbangan yang baik antara kinerja dan efisiensi daya, dengan konsumsi daya yang disesuaikan dengan intensitas tugas.Terutama berkaitan dalam prosesor dengan beban kerja yang berubah dengan cepat, DVF menuntut mekanisme umpan balik yang canggih untuk memantau kinerja sistem dan penggunaan energi, memberikan wawasan berharga untuk peningkatan di masa depan.Rasa harmoni dalam menyeimbangkan kinerja dengan penghematan kekuasaan dapat membangkitkan perasaan kepuasan yang mirip dengan menemukan keseimbangan dalam banyak tuntutan hidup.

Menimbang aplikasi praktis

Saat menerapkan teknik penskalaan tegangan ini, menilai trade-off sangat penting.Misalnya, mengurangi tegangan suplai meningkatkan efisiensi energi tetapi juga dapat memperlambat kecepatan operasi.Dengan demikian, menyeimbangkan penghematan energi dengan kinerja melalui pengujian sistem yang cermat dan penyempurnaan berulang menjadi yang terpenting.Selain itu, menggabungkan teknologi penskalaan tegangan adaptif meningkatkan metode ini dengan menyesuaikan diri dengan kondisi dunia nyata.Strategi yang mencakup semua ini menyoroti pentingnya adaptasi untuk mengoptimalkan sistem elektronik, menekankan bahwa menemukan efisiensi adalah perpaduan rumit dari wawasan teoretis dan aplikasi langsung.Saat jalan menuju efisiensi dinavigasi, orang mungkin merasakan kompleksitas dicerminkan dalam tarian halus antara teknologi dan ritme yang mendasari alam.

Pengaruh penumpukan transistor

Meluncurkan fenomena penumpukan

Pendekatan penumpukan transistor secara efektif mengurangi kebocoran subthreshold dalam serangkaian transistor.Konsep ini menjadi lebih menarik ketika beberapa transistor dimatikan secara bersamaan, menarik perhatian kita dan menarik eksplorasi lebih lanjut.

Memahami mekanisme dan efeknya

Pengaruh penumpukan berasal dari tegangan positif pada simpul menengah, yang membatasi aliran arus dan meningkatkan tegangan ambang batas karena tegangan negatif bulk-ke-sumber negatif.Sangat menarik untuk dicatat bahwa menambahkan lebih banyak transistor ke tumpukan semakin meningkatkan pengurangan kebocoran.Dalam konteks desain berdaya rendah, konfigurasi ini sangat berharga, terutama ketika efisiensi energi dikejar bersamaan dengan mempertahankan kinerja yang kuat.

Implementasi Praktis dalam Skenario Dunia Nyata

Solusi Rekayasa Seringkali memanfaatkan efek penumpukan saat merancang sirkuit dengan transistor secara seri, memanfaatkan sepenuhnya manfaatnya dalam meminimalkan kebocoran.Ini sangat bermanfaat di bidang -bidang seperti elektronik portabel dan sensor jarak jauh.Dalam domain ini, memperpanjang masa pakai baterai dan memastikan keandalan perangkat dianggap dengan harga tinggi karena dampaknya yang substansial pada kepuasan pengguna.

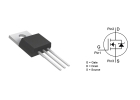

Gambar 5. Dua NMO Off-Transistor Stack

Penyesuaian ketebalan gerbang oksida

Scaling tujuan dan tantangan

Mengurangi ketebalan gerbang oksida adalah tugas yang dimotivasi oleh aspirasi untuk memperkuat kemampuan penggerak saat ini sambil meminimalkan tegangan suplai.Selain itu, strategi ini bertujuan untuk mengurangi efek saluran pendek, termasuk penurunan penghalang yang diinduksi drain, yang secara halus dapat mempengaruhi perilaku dan kinerja perangkat.

Efek penskalaan

Ketika lapisan oksida menjadi lebih tipis, medan listrik yang ditingkatkan muncul di atasnya.Bidang yang intensif ini, bersama dengan ketebalan oksida yang berkurang, dapat menyebabkan generasi arus bocor tunneling gerbang, yang dapat bergerak dalam dua arah: dari gerbang ke saluran dan sumber tumpang tindih sumber/tiriskan, atau sebaliknya, dari sumber/Tiriskan daerah tumpang tindih ke gerbang.

Representasi visual

Diagram di bawah ini menggambarkan jalur arus kebocoran gerbang oksida, menampilkan alirannya dari gerbang ke saluran dan sumber atau pembuangan area tumpang tindih di (a) dan pergerakannya dari sumber atau saluran tumpang tindih ke gerbang di (b).

Gambar 6. Arus kebocoran oksida gerbang dari gerbang ke saluran dan sumber atau saluran tumpang tindih di (a) dan sumber rom atau tiriskan area tumpang tindih ke gerbang di (b)

Menjelajahi dielektrik K tinggi untuk meningkatkan kinerja transistor

Reduksi arus kebocoran terjadi dengan mengganti SiO2 dengan gerbang alternatif dielektrik, langkah penting dalam inovasi.SI tegang dicapai melalui proses rumit dari secara aktif menekankan kisi silikon.Strain ini secara signifikan memperkuat efisiensi transistor dengan meningkatkan mobilitas saluran, dicapai dengan mengurangi berat badan NMOS dan laju dispersi interval elektron.Bersamaan dengan itu, ini menambah laju bobot pita dan laju dispersi pita lubang.Kemajuan semacam itu memicu minat karena dampaknya pada peningkatan fungsi perangkat.

Gambar 7: Mengilustrasikan perbandingan antara silikon konvensional dan silikon tegang.

Biasing tubuh

Di ranah elektronik, mengelola arus kebocoran adalah tugas yang membutuhkan pemahaman yang bernuansa tentang kekuatan halus yang berperan dalam transistor.Ini adalah tarian yang rumit, tindakan menerapkan bias tubuh terbalik (RBB), mengubah lanskap mode siaga yang tenang namun kompleks.Praktik ini menghargai harmoni antara komponen, mengoptimalkan tegangan ambang batas dan janji -janji efisiensi.

Pembiayaan Badan Terbalik, yang dianut dalam desain sirkuit terintegrasi (IC), dicari karena kemampuan mengurangi daya.Dalam metode ini, pilihan yang disengaja dibuat untuk menerapkan tegangan negatif tinggi melalui pompa muatan ke curah NMOS.Bersamaan dengan itu, PMOS curah dan n well menemukan koneksi mereka ke VDD Rail, jembatan yang memastikan kesesuaian dengan keadaan listrik yang diinginkan.Di sini, setiap pilihan mencerminkan strategi yang lebih dalam, satu tarian energi yang sering dipahami.

Distribusi jam

Eskalasi dalam penundaan kawat di samping peningkatan kapasitansi per unit area memperkuat tantangan yang terkait dengan latensi jam dan keuntungan yang diperlukan untuk jaringan jam.Ini lebih rumit oleh variasi dalam proses pembuatan, fluktuasi suhu, dan perubahan tegangan, yang membuatnya cukup rumit untuk mengelola kemiringan dan jitter secara efektif.

Pertimbangkan, misalnya, ketika jam menunjukkan latensi empat siklus dengan variasi penundaan 10%, itu menghasilkan kemiringan dan jitter sebesar 40% dari waktu siklus clock.Variabilitas di jitter yang disebabkan oleh kebisingan catu daya dapat mempengaruhi berbagai area chip.

Ada empat metode distribusi jam yang dibahas:

- Distribusi jam resonansi: Metode ini menyajikan pendekatan alternatif, berpotensi mengurangi waktu tidak dapat diandalkan dan mengurangi konsumsi daya.

-Distribusi jam gelombang berdiri: Diimplementasikan pada level papan dan chip, desain ini mencapai warna rendah dan rendah-jitter sambil menghemat daya karena resonansi antara kapasitansi jam dan induktansi kawat.

- Distribusi jam gelombang bepergian: Dengan menggunakan cincin saluran transmisi berpasangan, strategi ini menghasilkan jam dengan kemiringan minimal dan jitter, juga mengambil keuntungan dari manfaat daya yang disediakan oleh resonansi.

- Distribusi jam global muatan resonansi: Teknik ini melibatkan menciptakan fase yang konsisten dan amplitudo bentuk gelombang jam dengan menambah kisi dengan induktor yang beresonansi dengan kapasitansi beban jam.Pengurangan substansial dalam konsumsi jitter dan daya dicapai dengan meminimalkan kekuatan buffer jam yang menggerakkan beban resonansi.

Blog terkait

-

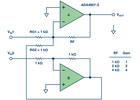

Dasar-dasar sirkuit op-amp

2023/12/28

Dalam dunia elektronik yang rumit, sebuah perjalanan ke misteri selalu membawa kita ke kaleidoskop komponen sirkuit, baik yang indah maupun kompleks.D... -

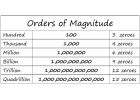

Berapa nol dalam sejuta, miliar, triliun?

2024/07/29

Juta mewakili 106, sosok yang mudah dipahami jika dibandingkan dengan barang sehari -hari atau gaji tahunan. Miliar, setara dengan 109, mulai meregang... -

Panduan Komprehensif untuk SCR (penyearah yang dikendalikan silikon)

2024/04/22

Silicon Controlled Rectifiers (SCR), atau Thyristors, memainkan peran penting dalam teknologi elektronik daya karena kinerja dan keandalannya.Artikel ... -

Baterai Lithium-Ion CR2032: Aplikasi Multi-Scenario dan Keuntungan Uniknya

2024/01/25

Baterai CR2032, baterai lithium-ion berbentuk koin yang umum digunakan, sangat penting pada banyak produk listrik berdaya rendah seperti jam tangan di... -

Transistor NPN dan PNP

2023/12/28

Untuk menjelajahi dunia teknologi elektronik modern, memahami prinsip -prinsip dasar dan aplikasi transistor sangat penting.Meskipun transistor tipe N... -

Apa itu termistor

2023/12/28

Di ranah teknologi elektronik modern, mempelajari sifat dan mekanisme kerja termistor menjadi upaya penting.Komponen elektronik presisi dan sangat mud... -

Jelajahi perbedaan antara PCB dan PCBA

2024/04/16

PCB berfungsi sebagai tulang punggung perangkat elektronik.Terbuat dari bahan non-konduktif, secara fisik mendukung komponen sementara juga menghubung... -

BC547 Transistor Comprehensive Guide

2024/07/4

Transistor BC547 umumnya digunakan dalam berbagai aplikasi elektronik, mulai dari amplifier sinyal dasar hingga sirkuit osilator yang kompleks dan sis... -

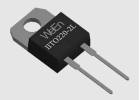

IRLZ44N MOSFET DataTheet, sirkuit, setara, pinout

2024/08/28

IRLZ44N adalah MOSFET N-Channel Power yang banyak digunakan.Terkenal dengan kemampuan switching yang sangat baik, sangat cocok untuk berbagai aplikasi... -

Apa itu sakelar solenoid

2023/12/26

Ketika arus listrik mengalir melalui koil, medan magnet yang dihasilkan menarik atau mengusir inti besi, menyebabkannya bergerak dan membuka atau menu...

Bagian panas

- DSPB56367PV150

- IDT74FCT2245ATQ

- TEA1101

- AM3354BZCZD60

- CL10CR82BB8NNNC

- GRM1556P1H6R6CZ01D

- AAT3190ITP

- NRF24LE1-F16Q32-R

- ELAG16AGZ

- ADG426BRS

- CRCW060310K5FKEA

- CM20MDI-12H

- RSM16312

- UPD70216HGF-10-3B9

- TMK063CH180JT-F

- 08055U121FAT9A

- PALCE22V10

- LM828M5/NOPB

- MC9RS08LA8CLF

- OPA680U

- PSB2160N

- 12065A101MAT2A

- 12062A152KAT2A

- 600S2R0BW250XT

- MCP4728A0T-E/UN

- RT0805DRE0736KL

- S29JL032J70TFI01

- AT27BV010-90VI

- DAC7811IDGSR

- S1D13775B00B60L

- ZL30150GGG2

- HI3716CRBCV10100

- AD5383BSTZ-3

- TPS2386BPW

- TAP106K006CRS

- GRM033R71A392KA01D

- AD8627AKSZ-R2

- PT2272-M4S

- T491B335M020AT7280

- T491D476M016AT7454

- T491C685K016AT2478

- T491X227K010AT2478

- 304-28-09-MC-0100F

- CS18LV10245CIR55

- LT1180IS

- AP7333-33SAG

- MT43A4G40200NFA-S15

- SKKT 280/22EH4